精簡(jiǎn)ISA總線Linux編程 – Part3

精簡(jiǎn)ISA總線接口是一種8-bit寬度的雙向并行擴(kuò)展總線,其特點(diǎn)是地址數(shù)據(jù)分時(shí)復(fù)用8位總線,加上4條總線控制信號(hào),即可實(shí)現(xiàn)對(duì)外部數(shù)據(jù)的快速讀寫。若再使能一條總線時(shí)鐘信號(hào)(共13條信號(hào)),就可實(shí)現(xiàn)高達(dá)10MB/s以上的數(shù)據(jù)傳輸。精簡(jiǎn)ISA總線作為英創(chuàng)主板的特色功能之一,在ESM6802、ESM7000、ESM7100、ESM335x等多款型號(hào)中均有配置。

關(guān)于對(duì)精簡(jiǎn)ISA總線接口的應(yīng)用編程的基本方法,請(qǐng)參考《精簡(jiǎn)ISA總線編程– Part 1》;應(yīng)用程序直接啟動(dòng)DMA做定長(zhǎng)數(shù)據(jù)的傳送方法,請(qǐng)參考《精簡(jiǎn)ISA總線編程– Part 2》。本文介紹由外部硬件觸發(fā)DMA傳送,應(yīng)用程序通過ISA驅(qū)動(dòng)(/dev/em_isa)讀取采集數(shù)據(jù)的方法。

硬件DMA的基本工作原理

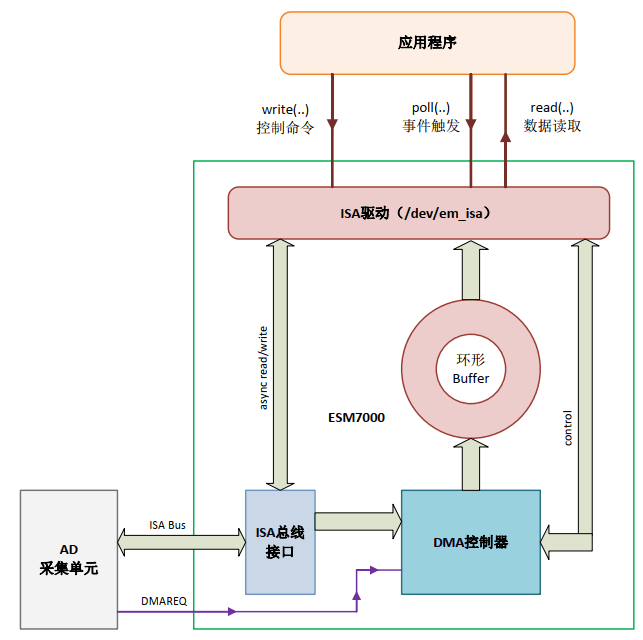

下圖是基于硬件DMA實(shí)現(xiàn)高速數(shù)據(jù)采集功能的系統(tǒng)框圖:

● 應(yīng)用程序通過常規(guī)的異步ISA讀寫操作,對(duì)AD采集單元進(jìn)行必要配置。

● 通過特殊的isa_write_buf(..)操作啟動(dòng)硬件DMA。

● 當(dāng)AD采集單元轉(zhuǎn)換數(shù)據(jù)準(zhǔn)備好,發(fā)出DMA請(qǐng)求信號(hào)(DMAREQ置高,脈沖寬度400ns – 1000ns)。

● DMA控制器感受到DMAREQ信號(hào),連續(xù)產(chǎn)生4個(gè)同步總線周期,讀取AD單元內(nèi)已準(zhǔn)備好的數(shù)據(jù),每個(gè)同步周期讀取2個(gè)字節(jié),共讀取8個(gè)字節(jié)。從DMAREQ請(qǐng)求開始,到DMA數(shù)據(jù)傳輸完畢,整個(gè)過程大約1840ns。之后DMA將等待一下一個(gè)DMAREQ脈沖信號(hào)。

● DMA讀取的數(shù)據(jù)將自動(dòng)存入驅(qū)動(dòng)程序內(nèi)部的環(huán)形Buffer中,當(dāng)DMA讀取的數(shù)據(jù)達(dá)到一定閾值(4KB)時(shí),驅(qū)動(dòng)將通過事件觸發(fā)應(yīng)用程序讀取整塊數(shù)據(jù)。

由于AD單元中的數(shù)據(jù)是通過DMA硬件存入系統(tǒng)緩沖區(qū)的,由此產(chǎn)生的CPU開銷就很低。應(yīng)用程序可在數(shù)據(jù)采集的同時(shí),完成必要的數(shù)據(jù)處理、顯示、通訊等功能塊。另一方面,由于AD采集單元不再需要保存轉(zhuǎn)換的數(shù)據(jù),可有效降低硬件成本。

實(shí)現(xiàn)基于硬件DMA的數(shù)據(jù)采集,需要以下信號(hào):

| ESM7000信號(hào)管腳 | 實(shí)際信號(hào)功能 |

ISA_AD0 | ISA地址數(shù)據(jù)總線,LSB |

| ISA_AD1 | ISA地址數(shù)據(jù)總線 |

ISA_AD2 | ISA地址數(shù)據(jù)總線 |

| ISA_AD3 | ISA地址數(shù)據(jù)總線 |

ISA_AD4 | ISA地址數(shù)據(jù)總線 |

| ISA_AD5 | ISA地址數(shù)據(jù)總線 |

ISA_AD6 | ISA地址數(shù)據(jù)總線 |

| ISA_AD7 | ISA地址數(shù)據(jù)總線,MSB |

ISA_CSn | ISA片選控制信號(hào)CS,低電平有效 |

| GPIO24 | ISA同步總線周期時(shí)鐘BCLK |

ISA_ADVn | ISA地址鎖存控制信號(hào)ADV,低電平有效 |

| ISA_RDn | ISA數(shù)據(jù)讀控制信號(hào)RD,低電平有效 |

ISA_WEn | ISA數(shù)據(jù)寫控制信號(hào)WE,低電平有效 |

| GPIO12 | DMA請(qǐng)求信號(hào)DMAREQ,輸入,高電平有效 |

注意:在使用硬件DMA數(shù)據(jù)傳輸時(shí),將禁止使用掛角GPIO12和GPIO24的GPIO功能、禁止使用CAN2端口。

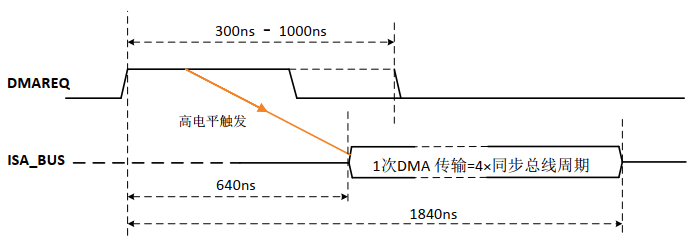

DMA傳輸總線時(shí)序說明

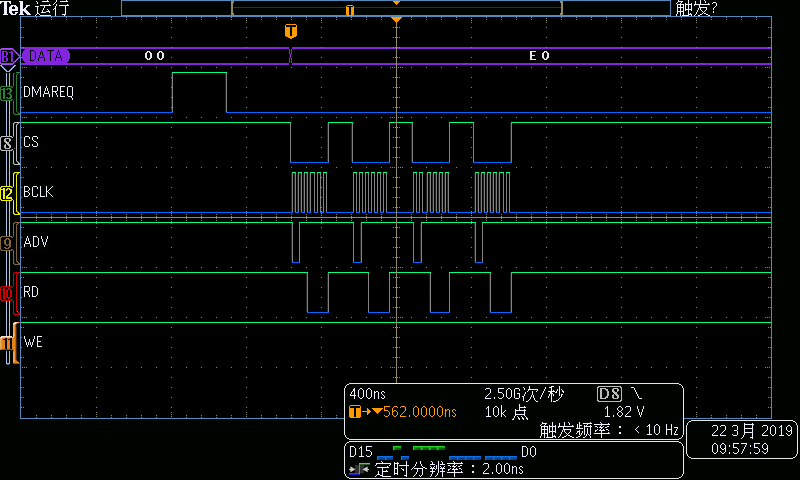

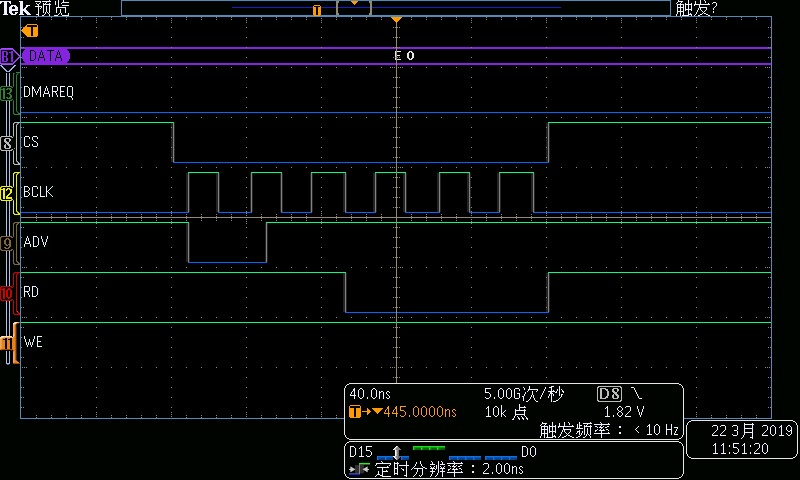

圖1是一次完整的DMA傳輸總體時(shí)序圖。

圖1 硬件DMA傳輸總線時(shí)序

從上面的時(shí)序可見,DMAREQ請(qǐng)求開始,到第一個(gè)總線周期,大約有640ns的延時(shí)。整個(gè)傳輸周期大約1840ns。按2000ns計(jì)算,采用硬件DMA傳輸,可實(shí)現(xiàn)每秒4MB字節(jié)的數(shù)據(jù)傳輸率。若假設(shè)4路模擬通道,每個(gè)樣點(diǎn)16-bit量化,這樣就對(duì)應(yīng)每通道500ksps的采樣率。這樣的采樣率可滿足絕大部分的工控應(yīng)用需求。展開圖1觀察,可見:

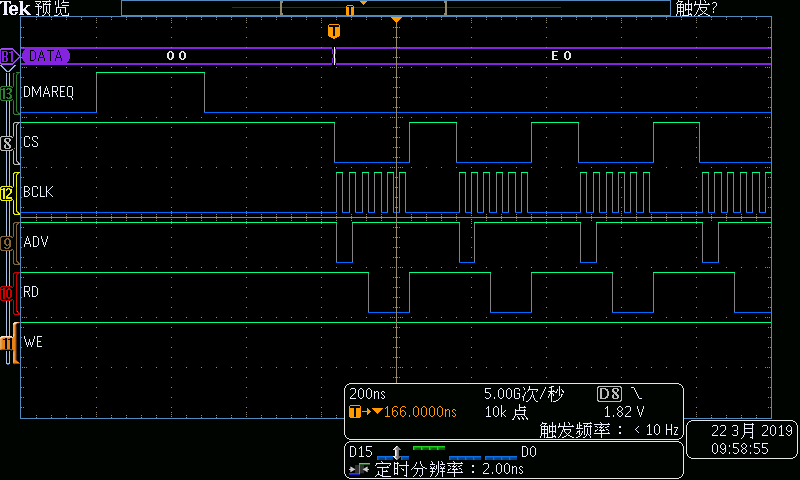

圖2 硬件觸發(fā)DMA傳輸時(shí)序前半部分

圖3 硬件觸發(fā)DMA傳輸時(shí)序后半部分

從上面的時(shí)序圖可見,有DMA啟動(dòng)的總線周期,每個(gè)周期只有6個(gè)BCLK脈沖,讀取2個(gè)數(shù)據(jù)字節(jié)。這與在《精簡(jiǎn)ISA總線編程– Part 2》中介紹的CPU啟動(dòng)的DMA操作不同。在使用時(shí)需特別注意。DMAREQ的脈沖寬度有一定要求:DMAREQ脈沖寬度應(yīng)大于240ns,才能保證可靠觸發(fā)DMA,其次DMAREQ應(yīng)在DMA傳輸周期結(jié)束前變低,否則可能誤觸發(fā)下一次DMA傳輸。

每個(gè)總線周期詳細(xì)的時(shí)序關(guān)系如下:

圖4 硬件觸發(fā)DMA總線周期時(shí)序

圖5 硬件觸發(fā)DMA總線周期時(shí)序參數(shù)標(biāo)注

為了簡(jiǎn)化AD采集單元的電路設(shè)計(jì),硬件觸發(fā)DMA傳輸總線周期輸出的地址固定在0xE0。AD采集單元的其他寄存器應(yīng)避免使用0xE0 – 0xE1這兩個(gè)地址。

應(yīng)用程序設(shè)計(jì)要點(diǎn)

應(yīng)用程序啟動(dòng)DMA數(shù)據(jù)傳輸,需要使用數(shù)據(jù)結(jié)構(gòu)struct isa_transfer的傳遞參數(shù)和數(shù)據(jù),struct isa_transfer的結(jié)構(gòu)定義如下:

structisa_transfer

{

void *rx_buf; /* != NULL: buffer for bus read */

void *tx_buf; /* != NULL: buffer for bus write */

unsigned len; /* buffer length in byte */

unsigned offset; /* offset,port address on isa bus */

unsigned inc; /* = 0: fixed offset, = 1: offset+1 after r/w */

}; 啟動(dòng)硬件觸發(fā)DMA傳輸,需要特殊的寫操作,代碼如下:

structisa_transfer t; // start ext-trigger dma memset(&t, 0, sizeof(structisa_transfer)); t.offset = 0x50E0; t.len = 0xFFFFFFFF; isa_write_buf(fd, &t);

注意在上述代碼中t.rx_buf和t.tx_buf均必須為空。停止硬件觸發(fā)DMA傳輸?shù)拇a為:

structisa_transfer t; // stopext-trigger dma memset(&t, 0, sizeof(structisa_transfer)); t.offset = 0x50E0; t.len = 0; isa_write_buf(fd, &t);

在啟動(dòng)DMA后,應(yīng)用程序的數(shù)據(jù)接收線程需調(diào)用poll等待數(shù)據(jù)ready的消息:

structpollfdfds[1];

fds[0].fd = fd;

fds[0].events = POLLPRI;

// wait data ready with timeout 2 seconds

if(poll(fds, 1, 2) == -1) {

perror("poll failed!\n");

goto error;

}

// data is ready…. 讀取數(shù)據(jù)的代碼為:

intrc, total_bytes;

structisa_transfer t;

externunsignedchargbuf[64 * 1024];

total_bytes = 0;

memset(&t, 0, sizeof(structisa_transfer));

// read data

t.rx_buf = gbuf;

t.offset = offset;

t.len = sizeof(gbuf);

rc = read(fd, &t, sizeof(structisa_transfer));

if(rc< 0) {

printf("%s dma data read failed %d\n", __func__, rc);

}

elseif(rc> 0) {

total_bytes += rc;

printf("%s dma data read %d\n", __func__, total_bytes);

}有興趣的客戶可與英創(chuàng)公司技術(shù)聯(lián)系,索取完整的測(cè)試代碼源碼。技術(shù)支持郵箱:support@emtronix.com。